Sa inžinjerske tačke gledišta, 1) mikroprocesor radi na osnovu kodiranih instrukcija, 2) da bi izvršio ono što instukcija od njega traži koristi kodirane podatke i 3) po potrebi odgovara na događaje iz spoljnog sveta.

Ponašanje mikroprocesora je definisano programom čiji se delovi (instrukcije) taktovano uzimaju iz programske memorije. Da bi neke od ovih instrukcija izvršio, mikroprocesor mora da koristi podatke koji se takođe nalaze u nekoj memoriji. Kod mikroprocesorskog sistema postoji samo jedna adresna magistrala i samo jedan magistrala za podatke na koju se povezuju i programska memorija i memorija za podatke. Obe memorije koriste istu magistralu za razmenu podataka sa mikroprocesorom formirajući von Neumann arhitekturu mikroprocesorskog sistema. Von Neumann arhitektura zahteva razdvajanje programa od podataka tako što se oni postavljaju u različite delove memorijskog prostora. Koristeći različite adrese, CPU zna da uskoro ka njoj stiže instukcija ili podatak Centralna procesorska jedinica dobija instrukcije iz memorije, dekoduje ih i sekvencijalno vrši preko instrukcija programirane zadatke. Po potrebi koristi i podatke koje uzima iz memorije za podatke. Sve se radi sekvencijalno u vremenu, skoro ništa ne može da se desi istovremeno u mikroprocesoru. Mikroprocesor konstantno ponavlja jedan isti ciklus operacija:

• Uzimanje instrukcije (fetching instruction phase)

• Dekodavanje instrukcije (decode phase)

• Izvršenje instrukcije (execute phase)

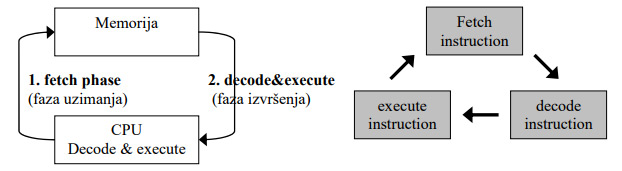

Osnovni instrukcijski “fetch–decode–execute” ciklus je prikazan na sledećoj slici br.1

Slika br.1 Fetch-decode-execute ciklus mikroprocesora.

Fetch–decode–execute ciklus se izvršava u ekvidistantnim vremenskim trenucima taktovanjem CPU (clock).

• Fetch phase CPU čita sledeću instukciju iz memorije i po njenom prijemu privremeno je sačuva u instrukcijskom registru (registar naredbi). Praćenje memorijske lokacije instrukcije koju treba izvršiti je toliko važno da svaka CPU ima za to specijalno dodeljen registar zvani programski brojač (PC –program counter). PC se uvećava za jedan svaki put nakon fetch faze i spremno pokazuje na sledeću lokaciju.

• Decode phase CPU dekoduje instukciju unutar registra naredbi i postavlja potrebne kontrolne signala. Za dekodovanje se koristi specijalni blok dekoder naredbi.

• Execute phase CPU izvršava instukciju i pri tom uglavnom koristi ALU (aritmetičku logičku jedinicu) i akumulator. Tip izvršenja zavisi od same instrukcije. Ukoliko je potrebno, CPU se ponovo obraća spoljnoj memoriji za podatke da bi prikupila za izvršenje potrebne promenjive. Na primer uzima promenjive A i B jer je dobila zadatka da ih sabere. Mikroprocesor mora posedovati specijalne interne registre koji služe za privremeno skupljanje potrebnih podataka za izvršenje raznih instrukcije (podatak stiže iz memorije ali pre izvršenja instrukcije ga treba negde privremeno smestiti unutar CPU)

Blok šema i način rada mikroprocesora

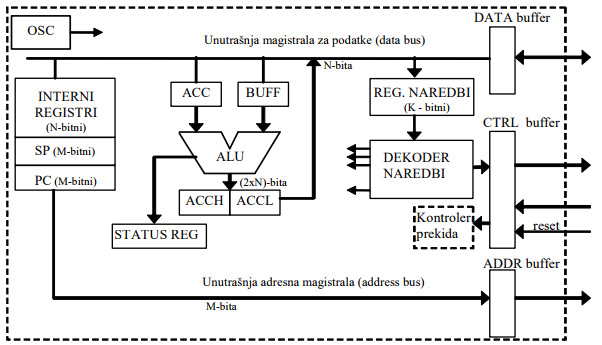

Mikroprocesor obuhvata sve funkcije centralne procesorske jedinice (CPU) u jednom integrisanom kolu i jeste centralna komponenta unutar jednog mikroprocesorskog sistema. Na slici br.1 data je blok šema jednog tipičnog mikroprocesora. CPU na sledećoj slici je generalizovana i smatra se da:

• obrađuje N-bitne podatke, N = 8, 16, 32, 64 bita.

• poseduje M-bitnu adresnu magistralu, i samim tim može da adresira maksimalno 2M različitih lokacija. Na primer u slučaju 10-bitne adresne magistrale imamo adresni prostor od 1Kb, 16 bitova 64 Kb, itd..

• obrađuje K-bitne instrukcije, sa povećanjem broja K se uvećava broj mogućih instrukcija, ali se ujedno i usložnjava tumačenje istih i usporava realizacija jedne instrukcije.

Slika br.2 Osnovna šema tipične centralne procesorske jedinice

Slika br.2 Osnovna šema tipične centralne procesorske jedinice

Delovi tipične centralne procesorske jedinice ili mikroprocesora

1. Programski brojač (PC counter). Programski brojač pokazuje na sledeću naredbu koju treba izvršiti (to je pointer na naredbu koji sadrži njenu adresu). U zavisnosti od potrebnog adresnog prostora to može biti 10, 12,16,24,32-bitni brojač. Obično su naredbe postavljaju u programsku memoriju u nizu sukcesivnih lokacija (jedna za drugom) pa se PC automatski inkremenira (uvećava za 1) kada se naredba izvrši. U slučaju da se program grana, jump, call instrukcije, ili dolaskom interrupt i reset signala u PC se upisuje nova adresa na koju se program grana. Start programa je neophodno linkovati na adresu na koju pokazuje PC nakon reseta, uobičajeno 0x0000 mada to zavisi od izbora proizvođača µC.

2. Registar naredbi. Neophodan za slučaj kada programske instrukcije i podaci dele istu magistralu. Ovaj registar prima novu naredbu i prosleđuje je ka dekoderu naredbi. Veličina registra je jednaka veličini jedne programske reči , naredbe, i može biti 8 bita, 16 bita, 24 bita ili više bita.

3. Dekoder naredbi Ovo je mozak CPU (centralna procesorska jedinica). Dekoder naredbi dekoduje naredbu i postavlja odgovarajuće kontrolne signale da bi se ova naredba izvršila. Postoje dve osnovne realizacije

3.1. Mikrokod Izvršenje naredbe se deli na mikroinstrukcije koje su upisane u internoj ROM memoriji. Novodošla naredba predstavlja ROM adresu na kojoj se nalazi mikro kôd, za izvršenje ove naredbe. Pri svakom jednom periodu clock signala izvršava se jedna mikro instrukcija zadavanjem odgovarajućih signala. Više mikroinstrukcija čini mikrokod jedne instrukcije. Mikrokod je sporiji (neophodno je više clock perioda za izvršenje cele naredbe) ali CPU sa mikrokodom može da postavi više kontrolnih signala u različitim vremenskim trenucima i time može da poseduje složenije instrukcije.

3.2. Kombinaciona mreža koja u jednom clock ciklusu dekoduje naredbu i postavlja sve potrebne kontrolne signale, čitanje (RD) registara je na pozitivnu ivicu clock signala, pisanje rezultata (WR) na negativnu.. Kombinaciona mreža je brža i naredbe se mogu izvršiti u jednom clock ciklusu ali realizacija je komplikovana i može ograničini količinu ostvarivih naredbi. Dekoder naredbi u oba slučaja generiše unutrašnje i spoljne kontrolne signale. Po završetku naredbe dekoder naredbi inkrementira ili upisuje novu vrednost u PC i ciklus se ponavlja.

4. Aritmetičko logička jedinica (ALU) i akumulator registar Akumulator je privilegovani interni registar CPU. Obično sadrži 8,16 ili 32 bita. U slučaju 16-bitnih procesora/DSP obično je 32-bitni da bi podržao operaciju 16-bitnog množenja, 16b x 16b = 32b. Ovaj registar je okružen krugovima za aritmetiku i logičke operacije (ALU) koji su sposobni da izvršavaju aritmetičke naredbe sabiranja, oduzimanja, množenja, inkrementiranja, dekrementiranja, negacije kao i logičke naredbe OR, AND, NOT, i druge. Uobičajeno je i da je moguće pomeranje (shift) bitova unutar akumulatora ulevo ili u desno za odreñeni broj mesta. Na kraju, često se i neke složenije IO naredbe referišu samo na akumulator (upis/čitanje u/iz spoljni RAM, na primer). Stanje akumulatora nakon neke instrukcije setuje odgovarajuće bitove (programske zastavice – flags) u statusnom registru. Parity, overflow etc.. Određeni kontrolni bitovi CPU definišu rad akumulatora, na primer da li se dozvoljava prekoračenje opsega (overflow) podatka nakon sabiranja / oduzimanja / pomeranja ili se podatak zadržava na limitu.

5. Statusni registar. Registar u kome se čuvaju programski flagovi čija vrednost uglavnom reflektuje stanje ALU ili podatka u akumulatoru.

6. Interni registri. Postoji odgovarajuće kašnjenje u izvršenju kôda svaki put kada se pristipa spoljnoj memoriji za podatke. Zato većina µC poseduje određenu količinu internih registara kojima se brže pristupa (registarsko adresiranje je u internoj i manjoj memorijskoj mapi) i koji su uobičajeno bolje povezani sa akumulatorom i sa ALU. U asembleru imamo punu slobodu da koristimo interne registre. Stvar je dobrog kompajlera i linkera za više programske jezike da iskoristi ove registre i da ubrzaju izvršenje programa. U C jeziku postoji i naredba register, koja obaveštava linker da mi želimo datu promenjivu da držimo u internom registru CPU.

7. Pokazivač stack-a (SP -stack pointer). Stack je skup sukcesivnih memorijskih lokacija (ne fiksan broj) u memoriji za podatke koje rade na principu LIFO (last in first out). Osnovna uloga stek memorije je da privremeno sačuva povratnu adresu programa koja se koristi nakon izvršenja podprograma ili prekida. Stek se takoñe koristi i da se privremeno sačuvaju registri i promenjive ili da se preko njega predaju argumenti pozvanoj fukciji. Sam pokazivač steka se uvećava sa svakim novim upisom na stek (push) i tako uvek pokazuje adresu na kojoj je trenutno vrh steka. U slučaju čitanja steka (pop) vrednost pokazivača steka se umanjuje za jedan. CPU može posedovati posebnu internu RAM memoriju predviđenu za stek ili je neohodno inicijalizovati i rezervisati odreñeni prostor u data memoriju za stek. U oba slučaja se mora znati koliko memorijskih lokacija je rezervisano za stack i paziti da se ne popuni. Stack se širi pri svakom pozivu podprograma, interruptu, kao i pri svakoj dodatnoj push naredbi i treba znati koliko će se maksimalno širiti (da ne prebriše neke druge podatke ili da drugi podaci ne prebrišu njega- program ne bi znao gde da se vrati). Ako nešto stavimo na stek moramo kasnije i da vratimo, inače se stack sa više takvih poziva širi.

8. Izlazni buffer-i Ovi registri služe da pojačaju signale na izlazu CPU, a u slučaju neaktivnosti odvajaju unutrašnju od spoljne magistrale.

9. Kontroler prekida Vrši obradu spoljnih prekida. Definiše njihov prioritet i dozvolu. U slučaju dolaska dozvoljenog prekida, obaveštava CPU koja prekida izvršenje tekućeg programa i izvršava prekidnu rutinu.