Vreme AD konverzije nije trenutno. Uobičajeno je mnogo duže od jednog ciklusa clock signala CPU. To znači da nije moguće u jednoj instrukciji startovati A/D konverziju, i u drugoj instrukciji već preuzeti gotov rezultat. Busy signal je upravo smišljen kao obaveštenje za CPU da podatak nije spreman. U prikazanom algoritmu CPU čeka da se stanje na busy liniji ne promeni, i tek onda preuzima podatak. Ovo se zove pulling A/D konvertora i jedno je od mogućih rešenja sinhronizacije CPU i konvertora. Ovo je prosto programsko rešenje, ali ujedno i veoma nepraktično jer CPU ne radi ništa čekajuči kraj A/D konverzije.

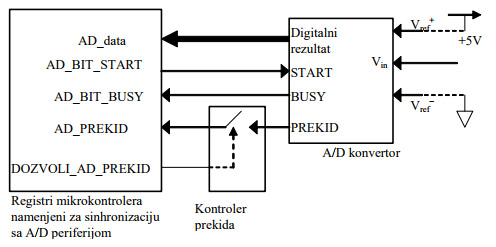

Proizvođači mikrokontrolera sa A/D ulazima nude i drugo rešenje, primenom sistema prekida. Pored busy signala, A/D blok poseduje i mogućnost generisanja signala prekida. Ovaj signal se generiše po završetku poslednje A/D konverzije i na taj način se obaveštava CPU da je podatak spreman. Ovo rešenje je složenije, ali mnogo optimalnije.

Da bi se ovo rešenje primenilo, prekid sa A/D konvertora se mora dozvoliti i mora se napisati odgovarajuća prekidna rutina za preuzimanje rezultata.

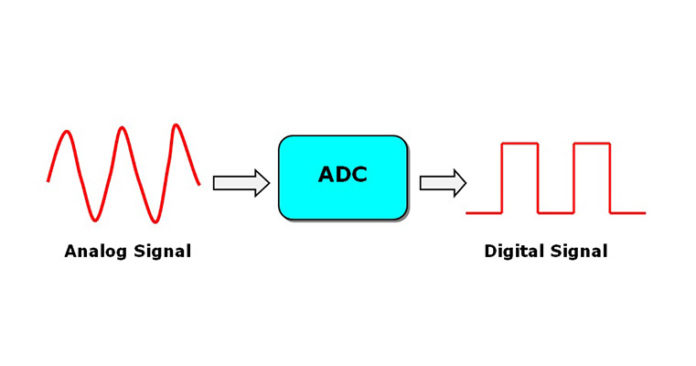

Slika br.1 Dva načina sinhronizacije CPU i A/D sistema

Primeri mašinskog programa za dva načina sinhronizacije CPU i A/D sistema

1. pulling porta

U ovom slučaju postoji samo glavni program:

setb AD_BIT_START ; Procesor inicira AD konverziju

wait_validAD: jnb AD_BIT_BUSY,wait_validAD ; Čeka da padne BUSY

mov Rezultat, AD_data ; uzima rezultat

(Ovaj prg. radi ali možda treba ukinuti signal AD_BIT_START da se ne ponovi A/D konverzija).

Dosta jednostavna realizacija (ne koristi se prekid i program se linearno izvršava u vremenu).Ali, gubi se vreme. Koristi se kad ionako nemamo šta da radimo ili kad vreme za rad nije kritično..Još primitivnija varijanta programa bi bila bez korišćenja BUSY signala. Umesto druge linije pišemo poziv na podprogram za fiksno vreme čekanja.

Icall DELAY_AD ; čeka neko vreme za koje je siguran da će AD da odradi

2. prekid AD konvertora

U glavnom programu se samo inicira AD konverzija:

setb AD_BIT_START ; Procesor inicira AD konverziju glavni program dalje ne gubi vreme, radi nešto drugo.

U prekidnoj rutini (prekid_AD) se preuzima rezultat:

prekid_AD: mov Rezultat, AD_data ; uzme rezultat

setb stigao_noviAD ; obaveštava da glavni prg. zna da je podatak spreman

reti ; povratak iz prekida

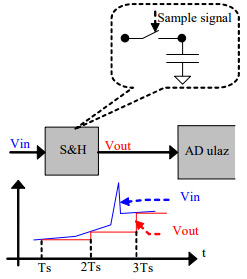

Sample & Hold kolo ADC sa metodom sukcesivnih aproksimacija

Da bi se pravilno izvršilo odabiranje signala koriste se sample& hold (S&H) kola. S&H kolo odabira signal (uzima odbirak) dovoljno brzo i drži ga dovoljno dugo (naboj kondenzatora) da se izvrši analogno-digitalna konverzija u samom ADC. S&H kolo se sadrži od kontrolisanog analognog prekidača i kondenzatora. Dok je prekidač zatvoren, kondenzator se puni na vrednost signala (sample process), kada se prekidač otvori, kondenzator zadržava (hold) odabrani nivo signala do sledećeg otvaranja. Kada je sample proces završen, dolazi do hold režima rada. Ako se signal u međuvremenu promeni, ta promena neće biti uočena. Vrlo je bitno odabrati periodu odabiranja (Ts) takvu da ne postoje značajne spektralne komponente signala koji želimo čitati na učestanostima većim od Niquistove učestanosti za tu periodu – 1/(2Ts).

Slika br.2 Prikaz S&H procesa

Mikrokontroler namenjen pogonima uobičajeno nema samo jedno, već više S&H kola. Ovo je veoma značajno u sistemima sa obaveznim simultanim odabiranjem dva ili više signala. Na primer, ukoliko imamo dve LEM sonde za čitanje struje motora, smeštene u dve faze motora, neophodno je njhove signale čitati istovremeno jer je samo tada moguće rekonstuisati struju treće faze. Ukoliko bi klasično izvršili odabiranje jednog po jednog kanala ne bi dobili rezultate u istom vremenskom trenutku (za N-tu veličinu bi odbirak zakasnio za prvom za N TADC). Zato je važno da u istom željenom trenutku sačuvamo sve analogne signale (S&H kolima) i zatim jedan po jedan obrađujemo u A/D konvertoru i prevodimo u digitalne reči. A/D konvertor će i dalje raditi sporo i signali se ne obrađuju u isto vreme, ali su odabrani u istom vremenskom trenutku. Bez S&H na svakom analognom ulazu ovo bi bilo nemoguće.

Uobičajen kompromis pri izradi mikrokontrolera je A/D koji poseduje dva S&H kola.

Ulazni analogni multiplekser u sklopu bloka za A/D konverziju

U digitalno regulisanom uređaju je uobičajeno potrebno meriti više analogoih veličina, kao na primer par struja, napona, temperatura, razne analogne reference, stvarna brzina, itd. Radi uštede u mikrokontroler se ugrađuje samo jedan A/D konvertor koji je povezan sa više analognih ulaznih pinova preko analognog multipleksera.

Osnovni dizajn softvera za rad sa A/D konvertorom ostaje isti, jedino je neophodno pre startovanja A/D konverzije selektovati željeni analogni kanal. Uštede sa ovakvom konfiguracijom (novčane i dimenzionalne) su velike a ograničenja minimalna jer obično i uzimamo jedan po jedan kanal a ne sve istovremeno. Ipak, u slučaju kritične brzine odabiranja, treba uvek uzeti u obzir da je vreme obrade u slučaju N kanala N puta veće nego u konfiguraciji sa N AD konvertora!! Ovaj problem se delimično umanjuje korišćenje sample&hold kola.

Moderni DSP uobičajeno poseduju dva ADC, svaki sa pridruženim S&H kolom i svojim analognim multiplekserom 8/1. Ovim se dobijaju 16 potencijalnih analognih ulaza, od kojih se po dva mogu čitati simultano (u istom trenutku).