Mehanizam koji omogućava pamćenje stanja u sekvencijalnim mrežama je povratna sprega, koja predstavlja povratni put signala od izlaza ka ulazima. Ovo je ujedno i kriterijum za razlikovanje kombinacione od sekvencijalne logike: graf koji predstavlja kombinacionu mrežu je obavezno acikličan, što znaći da u okviru mreže ne postoje zatvoreni ciklusi (putanje signala koje se posle prolaska kroz izvestan broj čvorova grafa, tj. logičkih kola vračaju u istu tačku). Korišenćjem povratnih sprega, moguće je realizovati osnovne memorijske elemente koji u sebi čuvaju 1 bit digitalne informacije.

Njihovim međusobnim spajanjem i kombinovanjem, realizuju se složenije sekvencijalne mreže i digitalni sistemi. Ovi osnovni elementi se nazivaju bistabilnim kolima. Njihov naziv upućuje na to da se ovakvi elementi uobičajeno nalaze u jednom od dva stabilna stanja (logička nula ili jedinica), a promene izmedu stanja se mogu vršiti isključivo dejstvom pobudnih signala na njihovim ulazima. Postoje dva osnovna tipa bistabilnih kola:

• Lečevi (eng. Latch) − transparentna kola, kod kojih je moguće menjati stanje u proizvoljnom vremenskom trenutku.

• Flipflopovi − sinhrona kola, kod kojih je moguće menjati stanje samo u trenucima kada to dozvoljava stanje na tzv. taktnom ulazu; upis se vrči na odgovarajuću promenu nivoa takt signala.

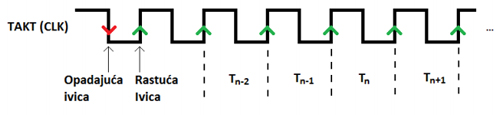

Kao što je već napomenuto, u digitalnim sistemima je uobičajeno korišćenje taktnog signala (eng. Clock). Ovaj signal predstavlja povorku pravougaonih impulsa, odnosno vrednosti 0 i 1, koje se međusobno smenjuju određenom frekvencijom. Uloga takta je sinhronizacija promena stanja flipflopova. Kod ivičnih flipflopova, promena stanja se vrši u trenutku odgovarajue promene na taktnom ulazu, što se naziva aktivnom ivicom takta. Dakle, ivični flipflopovi menjaju stanje na rastuću (uzlaznu) ivicu, odnosno promenu takta sa 0 na 1, ili na opadajuću (silaznu) ivicu, odnosno promenu takta sa 1 na 0.

Slika br.1 Takt signal

Pri analizi rada sekvencijalnih mreža, smatra se da takt diskretizuje vremensku osu. Stanja mreže se posmatraju tokom pojedinačnih perioda takta koje se obeležavaju celim brojevima (T0, T1, …, Tn). Početak svake periode određen je trenutkom pojave aktivne ivice takta. Stoga, uobičajeno je da se stanje izlaza memorijskog elementa Q tokom trenutno aktuelne periode takta obeležava sa Qn, stanje tokom prethodne periode je Qn − 1, a naredno stanje Qn + 1, itd. Na slici br.1 prikazan je taktni signal, sa obeleženim karakterističnim vremenskim trenucima.

SR-Leč

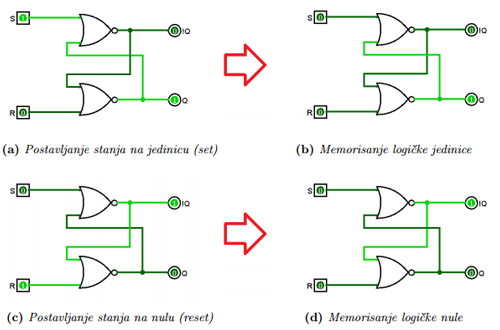

Osnovno i po strukturi najjednostavnije bistabilno kolo naziva se SR-leč. Sastavljeno je od 2 dvoulazna NILI kola sa ukrštenom povratnom spregom, kao što je prikazano na slici br.2. Izlazi kola su obeleženi sa Q i Q , što sugeriše da se očekuje da njihova stanja uvek budu komplementarna.

Opis ponašanja ovog bistabilnog kola kreće od situacije prikazane na slici 2a. Dovodenjem jedinice na S ulaz i nule na R ulaz, izlaz Q se postavlja na logičku jedinicu, uz istovremeno postavljanje Q na nulu. U ovom slučaju smatra se da je izvršeno postavljanje celog kola u stanje logičke jedinice (engl. Set). Ukoliko se nakon toga ulaz S postavi na logičku nulu, stanje kola će ostati nepromenjeno zahvaljujući dejstvu povratne sprege, kao što je prikazano na slici 2b. Slika 2c prikazuje postavljanje kola na logičku nulu (engl. Reset). Nakon toga, promena stanja R ulaza na nulu neće dovesti do promene na izlazima, ponovo usled delovanja povratne sprege (slika 2d). Ako se uporede slučajevi prikazani na slikama 2b i 2d, može se uočiti situacija koja je suštinski različita od one koja je karakteristična za kombinacionu logiku: iako su stanja na ulazima identična, stanja na izlazima se razlikuju u zavisnosti od toga u kom stanju se kolo prethodno nalazilo. Drugim rečima, kada su ulazni signali u stanju S = R = 0, kolo memoriše prethodno stanje. Da bi analiza ponašanja SR-leča bila kompletirana, potrebno je razmotriti još i poslednji slučaj, kada je S = R = 1. Prvi problem koji se javlja u ovom slučaju je to što izlazi Q i Q viˇse nisu komplementarni, pošto se na oba izlaza uspostavlja stanje logičke nule. Uz to, ako se odmah nakon toga oba ulaza promene na nulu, stanje na izlazima postaje nestabilno, nakon čega se uspostava jedno od dva stabilna stanja. Pri tome nije unapred poznato koje od stabilnih stanja će biti uspostavljeno. Zbog ovih neželjenih efekata, stanje na ulazima kada je S = R = 1 je zabranjeno, što znači da je pri projektovanju logike koja daje pobudu SR-leču potrebno voditi računa o tome da se ova kombinacija nikad ne pojavi na njegovim ulazima.

Slika br.2 SR-Leč

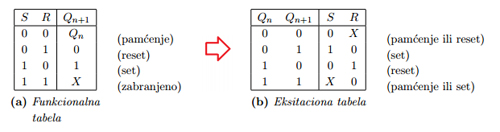

Ponašanje SR-leča, kao i drugih bistabilnih kola se uobičajeno opisuje pomoću dve tabele. Prva je funkcionalna, odnosno kombinaciona tabela, u kojoj je naredno stanje kola određeno u odnosu na trenutno stanje i stanja na ulazima. Na osnovu funkcionalne tabele izvodi se eksitaciona tabela, koja se naziva još i inverznom tabelom, odnosno tabelom pobude. Ova tabela za svaki mogući prelaz bistabilnog kola izmedu 2 stanja (ovih prelaza ima ukupno 4), daje odgovor na pitanje kakvu pobudu je potrebno dovesti na ulaze kola, da bi željeni prelaz bio ostvaren. Funkcionalna tabela SR-leča je prikazana na slici br.3a, a eksitaciona na slici br.3b.

Slika br.3 Funkcionalna i eksitaciona tabela SR-leča

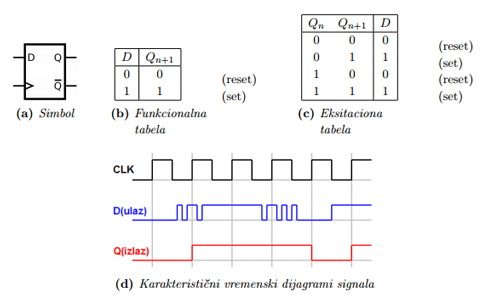

D-Flipflop

Flipflopovi su bistabilna kola koja imaju mogućnost promene stanja isključivo u trenucima pojave aktivne ivice takta (što se još naziva i okidanjem), u skladu sa stanjima na ulazima kola. Ova osobina ih čini sinhronim bistabilnim kolima. Po logici rada, najjednostavniji je D-flipflop: kod njega pored ulaza za takt postoji još jedan ulaz (D). Vrednost koja je postavljena na D ulaz se u trenutku okidanja upisuje u flipflop i odreduje njegovo stanje tokom predstoje´ce periode takta. Na ˇsematskom simbolu D-flipflopa prikazanom na slici br.4a, ulaz za takt je predstavljen trouglom1 . Funkcionalna tabela D-flipflopa je prikazana na slici br.4b, a eksitaciona na slici br.4c. Karakteristični vremenski dijagrami signala koji ilustruju rad D-flipflopa prikazani su na slici br.4d.

Slika br.4 D-flipflop

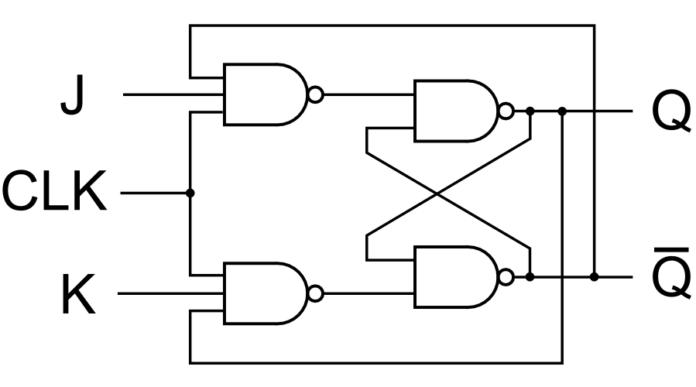

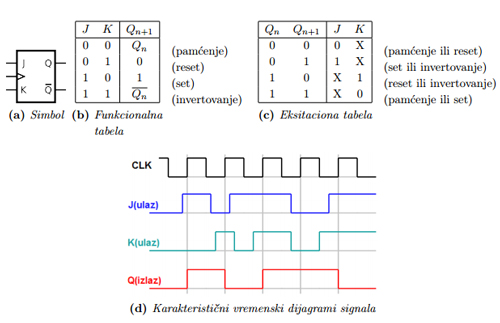

JK-Flipflop

JK-Flipflop ima 2 ulaza (J i K). Njegova funkcionalna tabela je slična kao kod SR-leč kola, izuzev u jednom detalju: Kombinacija kada su oba ulaza na logičkoj jedinici je dozvoljena i dovodi do invertovanja stanja kola. Slika br.5 prikazuje šematski simbol, funkcionalnu i eksitacionu tabelu JK- flipflopa i karakteristične vremenske dijagrame signala koji ilustruju njegov rad.

Slika br.5 JK-Flipflop

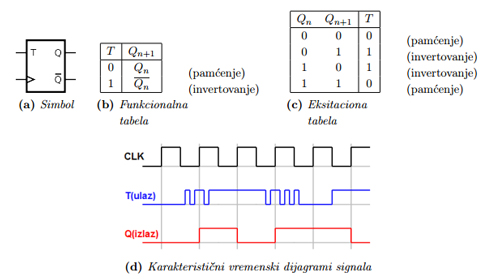

T-Flipflop

T-Flipflop ima jedan ulaz (T). Logika rada mu je takva da kada je T = 0, flipflop zadržava stanje u kojem se trenutno nalazi, a kada je T = 1, invertuje stanje. Slika br.6 prikazuje šematski simbol, funkcionalnu i eksitacionu tabelu T-flipflopa i karakteristične vremenske dijagrame signala koji ilustruju njegov rad.

Slika br.6 T-Flipflop